# ANALYTICAL STUDY OF ANALOG PHASE-LOCKED LOOP IN MESSAGE SIGNALS TRANSMISSION

Madhavi Marripally<sup>1</sup>, Dr Suchi Jain<sup>2</sup> Department of Electronics and Communication Engineering <sup>1,2</sup>OPJS University, Churu (Rajasthan)

#### ABSTRACT

A phase-locked loop is a criticism framework consolidating a voltage controlled oscillator and a phase comparator so associated that the oscillator frequency (or phase) precisely tracks that of an connected frequency-or phase-tweaked signal. Phase-locked loops can be utilized, for instance, to produce stable yield frequency signals from a settled low-frequency signal. The first phase-locked loops were executed in the mid 1930s by a French architect, de Bellescize. In any case, they just discovered expansive acknowledgment in the commercial center when coordinated PLLs progressed toward becoming accessible as generally minimal effort components in the mid-1960s. The phase locked loop can be dissected as rules as a negative criticism framework with a forward pick up term and an input term.

#### 1. INTRODUCTION

A modern propel technology in coordinated circuit technology makes fabrication processes exceptionally appropriate for digital outlines. Little territory and low-voltage plans are ordered by showcase prerequisites. Another favorable position of digital PLL is anything but difficult to update with the procedure changes. Since simple blocks are available in various digital and blended signal ICs, their overhaul is a vital factor in the arrival of another item. Nonetheless, the execution prerequisites of simple blocks requires a total upgrade in another procedure, along these lines expanding the outline process duration.

Decreasing the measure of simple circuitry can enhance the update of these blended signal ICs. A Phase Locked Loop is predominantly utilized with the end goal of synchronization of the frequency and phase of a privately created signal with that of an approaching signal. There are three components in a PLL. The Phase Frequency finder (PFD), the loop channel and the Voltage Controlled Oscillator (VCO). The VCO is the core of any PLL. The component by which this VCO works chooses the kind of the PLL circuit being utilized. There are essentially four sorts of constructing PLLs to be specific Direct PLL (LPLL), Digital PLL (DPLL) and All Digital PLL (ADPLL) [1].

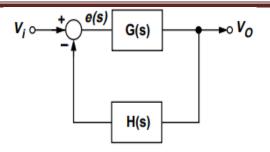

Figure 1. Standard negative-feedback control system model.

In a phase-locked loop, the error signal from the phase comparator is the contrast between the information frequency or phase and that of the signal input. The framework will compel the frequency or phase error signal to zero in the relentless state. The regular conditions for a negative-feedback framework apply.

Forward Gain = G(s), [s =  $j\omega = j2\pi f$ ]

Loop Gain =  $G(s) \times H(s)$

Closed Loop Gain G s GsHs - = + () 1 () ()

Because of the integration in the loop, at low frequencies the steady state gain, G(s), is high and VO/VI, Closed-Loop Gain = 1 H

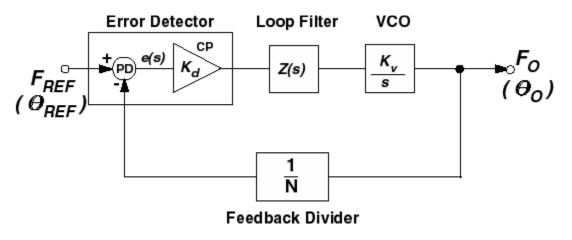

The components of a PLL that contribute to the loop gain include:

- 1. The phase detector (PD) and charge pump (CP).

- 2. The loop filter, with a transfer function of Z(s)

- 3. The voltage-controlled oscillator (VCO), with a sensitivity of KV/s

- 4. The feedback divider, 1/N

Figure 2.Basic phase-locked-loop model.

# IJITE Vol.03 Issue-02, (February, 2015) ISSN: 2321-1776 Impact Factor- 3.570

In the event that a linear component like a four-quadrant multiplier is utilized as the phase detector, and the loop channel and VCO are additionally simple elements, this is called a simple, or linear PLL (LPLL). In the event that a digital phase detector (EXOR door or J-K flip flounder) is utilized, and everything else remains the same, the framework is known as a digital PLL (DPLL).

In the event that the PLL is fabricated only from digital blocks, with no inactive components or linear elements, it turns into an all-digital PLL (ADPLL) [2].

Finally, with data in digital frame, and the accessibility of adequately quick handling, it is likewise conceivable to create PLLs in the product space. The PLL work is performed by programming and keeps running on a DSP. This is known as a product PLL (SPLL). Alluding to Figure 2, a framework for utilizing a PLL to produce higher frequencies than the info, the VCO sways at an precise frequency of  $\omega$ D. A bit of this frequency/phase signal is nourished back to the error detector, by means of a frequency divider with a proportion 1/N. This isolated down frequency is nourished to one contribution of the error detector. The other contribution to this illustration is a settled reference frequency/phase. The error detector thinks about the signals at the two sources of info. At the point when the two signal information sources are equivalent in phase and frequency, the error will be zero and the loop is said to be in a "locked" condition. In the event that we essentially take a gander at the error signal, the accompanying equations might be developed [3].

$$e(s) = F_{REF} - \frac{F_0}{N}$$

When

$$e(s) = 0, \frac{F_0}{N} = F_{REF}$$

Thus

$$F_0 = N F_{REF}$$

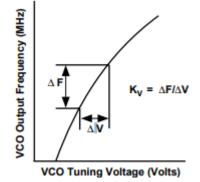

In business PLLs, the phase detector and charge pump together shape the error detector square. At the point when  $F_0 \neq N$   $F_{REF}$ , the error detector will yield source/sink current heartbeats to the low pass loop channel. This smoothes the present heartbeats into a voltage which thus drives the VCO. The VCO frequency will at that point increment or lessening as fundamental, by  $K_V \Delta V$ , where  $K_V$  is the VCO affectability in MHz/Volt and  $\Delta V$  is the change in VCO input voltage. This will proceed until e(s) is zero and the loop is locked. The charge pump and VCO therefore fills in as an integrator, trying to increment or diminishing its yield frequency to the esteem required in order to reestablish its contribution (from the phase detector) to zero.

A Monthly Double-Blind Peer Reviewed Refereed Open Access International e-Journal - Included in the International Serial Directories International Journal in IT and Engineering <u>http://www.ijmr.net.in</u> email id- irjmss@gmail.com Page 248

Figure 3. VCO transfer function

The overall transfer function (CLG or Closed-Loop Gain) of the PLL can be expressed simply by using the CLG expression for a negative feedback system as given above.

$$\frac{F_{0}}{F_{REF}} = \frac{Forward \ Gain}{1 + Loop \ Gain}$$

Forward Gain,  $G = \frac{K_{D}K_{V}Z(s)}{s}$

Loop Gain,  $GH = \frac{K_{D}K_{V}Z(s)}{N_{c}}$

When GH is much greater than 1, we can say that the closed loop transfer function for the PLL system is N and so

$F_{OUT} = N \times F_{Ref}$

# 2. PLL APPLICATIONS TO FREQUENCY UPSCALING

The phase-locked loop enables stable high frequencies to be produced from a low-frequency reference. Any framework that requires stable high frequency tuning can profit by the PLL method. Cases of these applications incorporate remote base stations, remote handsets, pagers, CATV frameworks, clock recovery and - era frameworks. A decent case of a PLL application is a GSM handset or base station. Figure 4 demonstrates the get segment of a GSM base station. In the GSM framework, there are 124 channels (8 clients for each channel) of 200-kHz width in the RF band. The aggregate bandwidth involved is 24.8 MHz, which must be examined for action. The handset has a transmit (Tx) scope of 880 MHz to 915 MHz and a get (Rx) scope of 925 MHz to 960 MHz. On the other hand, the base station has a Tx scope of 925 MHz to 960 MHz and a Rx extend of 880 MHz to 915 MHz. For this illustration, we will consider just the base station transmit and get areas. The frequency bands for GSM900 and DCS1800 Base Station Systems are appeared in Table 1. Table 2 demonstrates the channel numbers for the transporter frequencies (RF channels) inside the frequency bands of Table 1. Fl(n) is the inside frequency of the RF direct in the bring down band (Rx) and Fu(n) is the relating frequency in the upper band (Tx)

|          | T <sub>x</sub>      | R <sub>x</sub>      |

|----------|---------------------|---------------------|

| P-GSM900 | 935 to 960<br>MHz   | 890 to 915<br>MHz   |

| DCS1800  | 1805 to 1880<br>MHz | 1710 to 1785<br>MHz |

| E-GSM900 | 925 to 960<br>MHz   | 880 to 915<br>MHz   |

#### Table 1.1: Frequency Bands for GSM900 and Base Station Systems

#### **3. LITERATURE REVIEW**

The English physicist Edward Appleton initially portrayed the PLL and it showed up in the Proceedings of the Cambridge Philosophical Society in 1923. In 1953, Gruen distributed a paper particularly on the subject of automatic recurrence control use of PLL in shading TV transmission and gathering. In the year 1979, Gardner, F. examined insights about of PLL. He examined about fundamental standards of phase lock operation, ordinary practices of phase lock building and utilizations of phase lock to different issues. A compact audit of the fundamental PLL standards material to correspondence and control frameworks was displayed by Hsieh, G.C. and, Hung, J.C. in the year 1996.

#### 4. OBJECTIVES

The primary target of the proposed work is to display and mimic a moment arrange APLL in time space to ponder the accompanying:

- 1. To study the transient behavior of phase-locked loop in analog communication

- 2. To study the Analog Phase Locked Loop in time domain model

- 3. To study the multiplexing model and its techniques in analog communication

- 4. To study the dynamic parameters in multiplexing and phase-locked loop in analog communication

# 5. RESEARCH METHODOLOGY

The simulations are conveyed outing Turbo C and MATLAB stage. Turbo C is a compiler for C programming dialect from Borland. It was first presented in 1987 and it is noted for its coordinated improvement environment, little size and quick ordering speed. With Turbo C, there is no requirement for a different proofreader, compiler and linker to run the C programs. The primary focal points of C

codes are the enhanced precision and adaptability as nonlinear algebraic and differential conditions can be proficiently spoken to. The simulation speed can be essentially expanded by utilizing pre-assembled computer languages, for example, C. As C programming permits abnormal state displaying of useful pieces, along these lines, it is greatly useful for the framework level outline and optimization of framework parameters.

The methodology towards implementation of the proposed work for achieving the objectives as:

- **1.** Derivation of a theoretical model for second order APLL considering different block of elements.

- 2. Derivation of a theoretical model for circuit level simulation of the LF.

- **3.** Derivation of companion network model for non linear element of the LF based on Backward Euler numeric integration method.

- 4. Derivation of mathematical model for VCO and multiplier type PD of the model.

- 5. Derivation of a model for phase error process to study the cycle slips behavior of the model.

- 6. Derivation of an AWGN model for the APLL.

- 7. Derivation of a generalized model for the APLL considering different blocks.

- **8.** Simulation of the APLL model by using Turbo C program to study the dynamic characteristics of the PLL and effects of noise on the system.

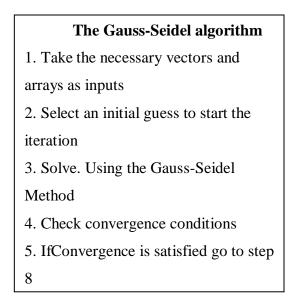

We are using following tools & methods in our research work:

• Design of an algorithm for the proposed APLL model for simulation in time domain using the Gauss-Seidel iterative method.

- Developing the simulation program incorporating iterative solution options for adjustment of convergence condition, Tsim, T, absolute relative error and tolerance value.

- Developing the simulation program for studying the effects of noise on APLL dynamics.

- Developing the simulation program to study the RMS, histogram and PE) F of phase error behavior.

- Simulating the model to plot the time-domain voltage waveforms of the APLL model.

- Simulating the model to extract the phase and frequency information from time-domain voltage waveforms of the model. The next chapter of the thesis will present in details the theoretical estimation for the proposed APLL model.

# 6. RESULTS

Phase frequency detector and DCO reproductions are finished utilizing Xilinx and reenactment waveform of same is appeared beneath. The outline has been finished remembering the versatility, adaptability and optimal standard. It can be utilized as a part of any outline suiting the given frequency determinations. A framework clock of 5 MHz is utilized. The plan is executed for a middle frequency of 300 kHz. It's chiefly implied for low frequency applications. The present outline offers a working frequency scope of 290 kHz to 320 kHz around. The outline can be stretched out past that too. Be that as it may, the rationale model should be changed to overcome the proliferation defer that is acquainted due with more noteworthy number of bits engaged with the calculation.

# 7. CONCLUSION

As indicated by audit of ADPLL, digital circuits are more adaptable, proficient, adaptable, and less loud as contrasted with simple circuit. This paper talks about the ADPLL configuration utilizing Verilog HDL It likewise displays the FPGA execution in detail. The ADPLL blocks utilized for the outline are additionally given here. This PLL is intended for the middle frequency of 200 kHz and its working frequency scope of ADPLL is 189 kHz to 215 kHz, which is the bolt scope of the plan. At the point when the info was to blame, it consequently continued output arrangement by utilizing the last known right parameters.

# REFERENCES

- 1. Perrott, M.H., "Fast and Accurate Behavioural Simulation of Fractional-N Frequency Synthesizers and other PLL/DLL Circuits," Proceedings of the IEEE/ACM Design Automation Conference, pp. 498-503, June 2002.

- 2. Fan, Y., "Modeling and Simulation of £A Frequency Synthesizers," Proceedings of the IEEE Symposium on Industrial Electronics , Vol. 1, pp. 684-689, June 2001

- 3. De, B. and Sarkar, B.C., "A novel quick response charge pump phased lock loop", Indian journal of engineering and material science, vol.18 December, 2008, pp. 473-482.

- J Lee, j., Su, Y. and Shen, C., "A Comparative Study of Wireless Protocols: Bluetooth, UWB, ZigBee, and Wi-Fi", The 33rd Annual Conference of the IEEE Industrial Electronics Society (IECON) Nov. 5-8,2007, Taipei, Taiwan 1-4244-0783-4/07/\$20.00 ©2007 IEEE

- 5. Yahya,A., Sidek,O. and Saleh,J., "Design and Develop Wireless System Using Frequency Hopping Spread Spectrum", Engineering Letters, November 2006

- 6. Baneijee, D., "PLL Performance, Design and Simulation", National Semiconductor, 1998.

- 7. Tomasi, W.: 'Advanced Electronic Communication Systems', Pearson Education, Sixth Edition, 2004

- 8. Lathi, B.P. and Ding, Z.: 'Modem Digital and Analog Communication Systems', Oxford University Press, New York, 2010.

- 9. Appleton, E.V., "Automatic Synchronization of Triode Oscillators", Proceedings of Philosophical Society ,Vol.21, no.III, pp 231-248,1922-23 [31]

- 10. Gruen, W.J., "Theory of AFC Synchronization", Proceedings of IRE, pp 43-76, August 1953

- 11. Margaris, N. and Mastorocostas, P., "On the nonlinear behaviour of the analog Phase-Locked Loop: Synchronization", IEEE Transactions on Industrial Electronics, Vol. 43, No.6, December 1996

- 12. Lee, T. and Razavi, B., "A Stabilization Technique for Phase-Locked Frequency Synthesizers", Symposium on VLSI Circuits Digest of Technical Papers, 2001

- 13. Swanepoel, H.R. and Sinha, S., "A Design of a Frequency hopping spread spectrum Transceiver for cellular systems", 2004 IEEE, AFRICON, vol.97 (3).

- 14. Keaveney, M., Walsh, P., Tuthill, M., Lyclen, C. and Hunt, B., "A IOps fast switching PLL synthesizer for a GSM/EDGE base-station", Solid-State Circuits Conference, 2004. Digest of Technical Papers, ISSCC, 2004 IEEE

- 15. Herzel, F. and Piz, M., "System-Level Simulation of a Noisy Phase-locked Loop", 13th GAAS Symposium-Paris, 2005, pp. 193-196