# **RECENT TRENDS OF POWER DELAY FOR LOW POWER & HIGH SPEED VLSI CIRCUITS**

#### BukyaBalaji<sup>1</sup>, Dr. Yash Pal Singh<sup>2</sup>

#### **Department of Electronics and Communication Engineering**

## <sup>1,2</sup>OPJS University, Churu (Rajasthan)

#### Abstract

This paper, introduces an idea of the power improvement hypothesis approach, the estimation systems and streamlining circuits utilized for low power VLSI circuits. In more up to date advancements, power is an essential plan requirement. Control dissemination has soar because of transistor scaling, chip transistor tallies and clock frequencies. Effective chip configuration requires low power thought, and assurance of the areas (spots) on the pass on where control dissemination happens. The requirement for low power configuration is additionally turning into a noteworthy issue in superior computerized framework, for example, chip and advanced incorporated circuits. The approach which we use for low power circuits traverses a wide range from gadget or process level to calculation level.

Keywords- optimization, VLSI, switching power, short circuit, leakagepower, voltagescaling, subthresholdleakage, pipeliningapproach, parallel processing approach, switched capacitance, clock gating

#### **1. INTRODUCTION**

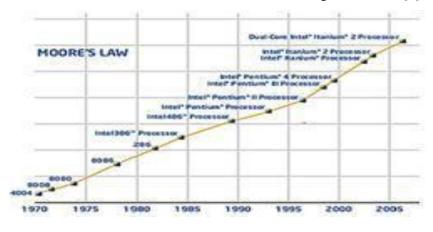

In prior outline territory, execution, cost and dependability was the significant issue and thought was of just auxiliary power importance. The improvement of aggressive market segments, for example, remote applications, tablets, and versatile medicinal relies on upon gadgets, the power dissemination as the most vital parameter inlight of the fact that the development rate of the battery innovations is not all that promising. As indicated by Morre's law semiconductor innovation will twofold in each 18 months.& at the same time gadget number and clock recurrence are expanding exponentially subsequently Power dispersal is perceived as a basic parameter in current VLSI configuration field because of high chip thickness and high recurrence[1].

A Monthly Double-Blind Peer Reviewed Refereed Open Access International e-Journal - Included in the International Serial Directories International Journal in IT and Engineering http://www.ijmr.net.in email id- irjmss@gmail.com

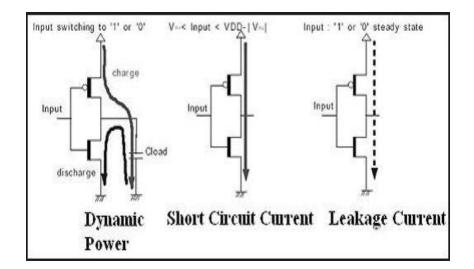

The average power consumption in CMOS circuits consists of I) Dynamic or switching power consumption II) Short circuit Power consumption III) Leakage power consumption IV) static power consumption[2].

#### A. Dynamic(switching) Power Dissipation

Dynamic power scattering can be further subdivided into three instruments: exchanged,

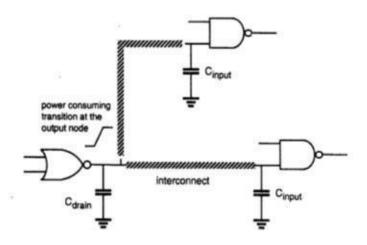

short out, and glitch control dissemination. Every one of them pretty much relies on upon the movement, timing, yield capacitance, and supply voltage of the circuit. The rehashed charging and releasing of the yield capacitance is important to transmit data in CMOS circuits. This charging and releasing of the hub capacitances foundations for the exchanged power dissemination[3].

Figure 2: A NOR gate driving two NAND gate through interconnection lines

# **B.** Short Circuit Power Dissipation

C. In genuine circuits signals have non-zero ascent and fall times which causes both the P net and the N net of the CMOS door to direct current all the while that implies both nmos and pmos transistors may lead all the while for short measure of time amid exchanging .This current does not add to the charging of capacitance in the circuit ,it is called hamper utilization, This segment is particularly common if the yield stack capacitance is little and/or if the info flag rise time and fall times are substantial[4].

#### D. Leakage Power Dissipation

In genuine circuits signals have non-zero ascent and fall times which causes both the P net and the N net of the CMOS door to lead current at the same time that implies both n 'mos' and p 'mos' transistors may direct at the same time for short measure of time amid exchanging .This current does not add to the charging of capacitance in the circuit ,it is called impede utilization, This segment is particularly pervasive if the yield stack capacitance is little and/or if the info flag rise time and fall times are vast[5].

A Monthly Double-Blind Peer Reviewed Refereed Open Access International e-Journal - Included in the International Serial Directories International Journal in IT and Engineering http://www.ijmr.net.in email id- irjmss@gmail.com

## D. Static Power dissipation

The static power parts wind up noticeably critical when the circuits are very still, i.e. at the point when there is no action in the circuits and they are altogether one-sided to a particular The static power dissemination state. incorporates sub edge and switched one-sided

diode spillage streams. Because of the fundamental however destructive (in a spillage control sense) down-scaling of edge voltages, the sub edge spillage is winding up noticeably more articulated. Beneath the edge voltage, in feeble reversal, the transistors are not totally off. The sub edge current has a solid reliance on the edge voltage [6].

**Figure 3: Power Dissipation**

$P = \alpha f CL VDD^2 + VDDIshort-circuit + VDDIleakage + VDDIstatic$

Where f is the clock recurrence, C is the normal exchanged Capacitance per clock cycle, VDD is the supply voltage, Short-circuit is the short out current and Leakages the spillage current. In a very much enhanced low power VLSI circuits, the 1st expression of this condition is by a wide margin the overwhelming. The standby power utilization is represented by the third term. Utilizing a lower VDD is a viable approach to decrease the dynamic power utilization since 1st term is relative to the square of VDD.It ought to likewise be noticed that the short out and spillage control scattering are additionally unequivocally reliant on VDD.However, utilizing a lower VDD corrupts execution[7].

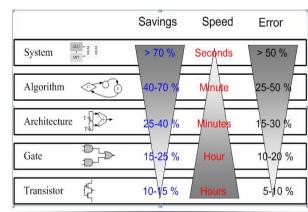

# 2. OPTIMIZATION AT VARIOUS LEVEL OF ABSTRACTION

An integrated lowpower methodologyrequires optimizationat all design abstraction layers as mentioned below.

- 1. System: Partitioning, Power down

- 2. Algorithm: Complexity, Concurrency, Regularity

- 3. Architecture: Parallelism, Pipelining, Redundancy, Data Encoding

- 4. Circuit Logic: Logic Styles, Energy Recovery, Transistor Sizing

A Monthly Double-Blind Peer Reviewed Refereed Open Access International e-Journal - Included in the International Serial Directories International Journal in IT and Engineering http://www.ijmr.net.in email id- irjmss@gmail.com

Reduction.

#### 5. Technology: Threshold

#### **Figure 4: Different level of Abstraction**

#### A. System level

Exact power examination devices are accessible at circuit or door level however not for framework level. The target capacities for apportioning have been the cut-measure as well as the circuit delay while the requirements have been I/O stick tally per square and piece estimate. Apportioning for low power has as of late turned into an essential issue[8].

#### B. Algorithm level

Here behavioral showing is joined It implies the path toward mapping an irregular state assurance of an issue into enroll trade level arrangement.

#### C. Architecture levelPipelining

In this approach both information &output vectors are inspected through enroll cluster and driven

By a clock flag- By utilizing pipeline structure the supply voltage will be diminished however while exchanging off territory for lower control, this approach additionally builds the inertness yet inactivity is not a noteworthy concern Parallel Processing approach (Hardware Replication) Parallelism is likewise utilized for exchanging off zone for low power dispersal[10].

ISSN: 2321-1776

Multithreshold Devices.

#### D. Circuit level

#### Transistor sizing

Transistor estimating in a combinational entryway circuit can have critical effect on circuit deferral and power dispersal. On the off chance that the transistors in a given door are expanded in size, then the deferral of the entryway diminishes. Encourage, the deferral of the fanin entryways expands in light of expanded load capacitance[9].

# E. Technology level

#### **Multiple Thresholds**

Modern processes can build transistors with different thresholds. Power can be saved by using a mixture of CMOS transistors with two or more different threshold voltages. In the there are two different simplest form

thresholds available, common called High-V<sub>t</sub> and Low-V<sub>t</sub>where V<sub>t</sub> stands for threshold voltage. High threshold transistors are slower but leak less, and can be used in non-critical circuits[10].

# 4. OPTIMIZATION TECHNIQUES FOR LOW POWER VLSI

There is no general system to cut tradeoffs between power utilization, deferral and region thus architects are required to choose appropriate and proficient strategies that fulfill application and item needs[11]. Lessening of exchanging limit, clock gating Reduction of exchanged capacitance Voltage Scaling

- Reduction of exchanged capacitance: Decreasing the exchanged capacitance is comparable power productive as lessening the clock recurrence of circuit. Many propelled systems have been proposed to decrease the exchanged capacitance. The determination of rationale style can essentially influence the basic capacitances. At whatever point allowcontrol arrangement is looked for, traditional static CMOS is frequently a protected and proficient and Multiplexers as well as doors are a special case since they can be executed in pass-transistor rationale styles utilizing fewer transistors. In fliptumbles and registers, the capacitance of the clock hubs is vital since the clock flag has a high movement. In this way, he flip-flops with few timed transistors have been proposed.

- Clock gating: It is known as clock recurrence decrease and for the most

part utilized as a conjunction with other low power methods.

Voltage scaling: lt is more advantageous than clock gating .Pipelining and Hardware replication approach is utilized for voltage scaling .Control scattering of all the four parts rely on upon supply voltage, Hence voltage scaling is the appealing answer for decreasing it yet sub limit spillage will increment exponentially.

## 5. OPTIMIZATION CIRCUITS USED IN VLSI

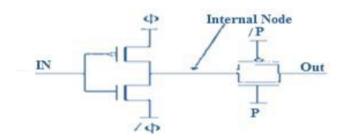

#### Adiabatic logic circuit

The term adiabatic is frequently used to depict thermodynamic strategies that have no essentialness exchange with nature consequently no imperativeness setback as warmth .Hence adiabatic method of reasoning gives the probability of reusing or reusing, a bit of the imperativeness drawn from the impact supply Adiabatic basis works with trading practices which reduces the impact by giving set away essentialness back to the supply. Thusly, the term adiabatic reason is used as a piece of low-power VLSI circuits which realizes reversible basis. In this, the major framework changes are occupied with power clock which accept the key part in the rule of operation. Diodes are not used in the blueprint of Adiabatic because of thermodynamically Logic irreversible nature Each time of the power clock offers customer to achieve the two essential arrangement rules for the adiabatic circuit arrange.

Ex SZ Never turn on a transistor if there is a voltage transversely over it (VDS> 0) never execute a transistor if there is a current through it (IDS  $\neq$  0)

A Monthly Double-Blind Peer Reviewed Refereed Open Access International e-Journal - Included in the International Serial Directories International Journal in IT and Engineering http://www.ijmr.net.in email id- irjmss@gmail.com

Never go current through a diode If these conditions as for the commitments, in all the four times of drive clock, recovery stage will restore the essentialness to the influence clock, coming to fruition great imperativeness sparing cash on real data, the pass portal is turned on by a little bit at a time swinging P and/P. Rails f

and/f"split", well ordered swinging to breaking point voltage (V<sub>dd</sub>) and Gnd. Pass passage is slaughtered when yield is reviewed,. Internal center is restored by gradually swinging f and  $V_{dd}/2$ .Once the electronic contraption is turned on imperativeness move occurs controlled so that there is no potential drop over the device.

Figure 5: Charge Recovery Logic

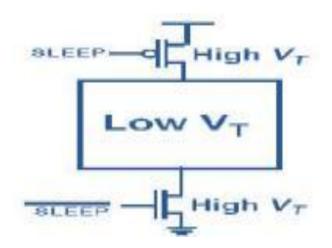

#### A. Sleep transistor

The static power can be decreased by using rest transistors. Sleep Transistors are High Vt transistors related in course of action with low Vt method of reasoning as showed as takes after .When the essential circuit involving Low Vt devices are ON the rest transistors are also

ON realizing normal operation of the circuit. Since High cutoff (Vt )is related in course of action with Low edge (Vt) circuit the spillage current influence mishap is measured by High edge (Vt) contraptions and is peaceful low.Therefore, the resultant static impact dispersal is diminished.

Figure 6: Sleep transistor

A Monthly Double-Blind Peer Reviewed Refereed Open Access International e-Journal - Included in the International Serial Directories International Journal in IT and Engineering http://www.ijmr.net.in email id- irjmss@gmail.com

### **5. CONCLUSION**

Here we have examined the idea of energy improvement, its strategies and the circuits we utilized for this. Bringing down power scattering at all reflection levels is a concentration of extreme scholarly and modern research. A decrease of any parameters like information rise time, source spillage current, Gate current, Switching power, hamper, control scattering capacitance, and yield stacking influence is helpful for us and, gives minimal effort item to the shopper

#### REFERENCES

- 1. M. Jasmin,"Optimization Techniques for Low Power VLSI Circuits" Middle-East J. Sci. Res., 20 (9): 1082-1087, 2014.

- 2. Kumar Saurabh, Prashant Mani," A REPORT ON LOW POWER VLSI CURCUIT DESIGN", Volume-1, Issue-1 January 2014, PP:178-184.

- 3. Amit Singh Gaur, JyotiBudakoti,"Energy Efficient Advanced Low Power CMOS Design to reduce power consumption in Deep Submicron Technologies in CMOS Circuit for VLSI Design", International Journal of

- 4. Advanced Research in Computer and Communication Engineering Vol. 3, Issue 6, June 2014, PP:7000-7008.

- 5. Nisha Sharma, ManmeetKaur,"A Survey of VLSI Techniques for Power and Estimation of Optimization Optimization", IJETAE Volume 4, Issue 9, September 2014) me 4, Issue 9, September 2014, PP: 351-355.

- 6. S. M. Kang and Y. Leblebici. CMOS Digital Integrated Circuits: Analysis and

Design. McGraw-Hill Companies, Inc. 1996

- 7. J.C. Park, V. J. Mooney III and P. "Sleepy Pfeiffenberger, Stack Reduction Leakage Power," of Proceeding of the International Workshop on Power and Timing Modeling, Optimization andSimulation, pp. 148-158, 2004.

- 8. Gordon E. Moore. Cramming more components onto integrated circuits. Electronics, 38(8), April 1965.

- 9. ArjitRaychowdhury, SaibalMukhopadhyay, and Kaushik Roy. "Modeling and estimationof leakage in sub90nm devices" In Int. Conf. VLSI Design, pages 65-70, 2004.

- 10. Agarwal et al."Leakage power analysis and reduction: models, estimation and tools"IEEE Proc. Comput.Digit. Tech., 152(3):353-368, May 2005.

- 11. S.Samanta" Power Efficient VLSI Inverter Design using Adiabatic Logic and Estimation of Power dissipation using VLSIEDA Tool" Special issue of International Journal of computer communication Technology.vol 2.isuue 2,3,4.pp300-303. 2010

A Monthly Double-Blind Peer Reviewed Refereed Open Access International e-Journal - Included in the International Serial Directories International Journal in IT and Engineering http://www.ijmr.net.in email id- irjmss@gmail.com